Опыт реализации системы верификации, управляемой тестовым покрытием

Верификация предполагает проверку соответствия системы требованиям ее спецификации на каждом уровне детализации [1]. На уровне RTL-описания система задается исходным кодом, на основании которого генерируется RTL-модель. При определенной сложности, свойственной реальным системам, формальные методы не применимы для такой проверки RTL-описания, т.к. сопряжены с чрезвычайно высокой вычислительной сложностью. На практике в этом случае используется проверка RTL-кода устройства посредством подачи тестовых стимулов на RTL-модель и контролем отклика на соответствие либо непосредственно спецификации, либо эталонной модели. Применяемые методики написания и генерации тестов не имеют априорных гарантий покрытия всех возможных ситуаций, позволяющих выявить ошибки в дизайне. Для вывода о степени готовности дизайна к выпуску требуется оценка доли тех ситуаций, которые не были покрыты тестами.

С точки зрения того, кто контролирует соответствие (верификатора), тестовое покрытие должно обеспечивать максимальную вероятность обнаружения ошибок при минимальной затрате труда и вычислительных ресурсов [2]. В то же время, формализованной функции, удовлетворяющей данным требованиям, не существует. С формальной точки зрения тестовое покрытие – подмножество ситуаций некоторого класса, реализованных при подаче последовательности тестовых воздействий на входы тестируемой системы, при этом величина тестового покрытия задает долю реализованных ситуаций этого класса. Величина покрытия, рассматриваемая применительно к конкретному классу ситуаций, называется его метрикой покрытия. Предполагается, что существует корреляция между числом ненайденных ошибок и отличием величины покрытия от единицы, и хотя для наиболее распространенных метрик нет строгого доказательства этого предположения, метрики покрытия широко используются для оценки качества верификации, благодаря возможности автоматизации их измерения [3].

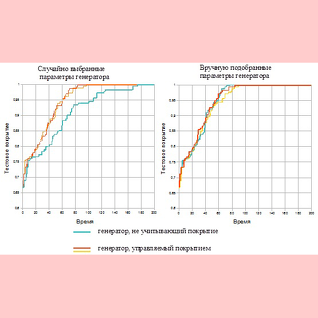

В традиционных схемах генерации тестов подсчет покрытия производится после исполнения теста или пакета тестов. Для достижения требуемого покрытия изменяются настройки генератора тестов или модифицируются сами тесты, т.е. обратная связь осуществляется через верификатор. В то же время управляемая покрытием генерация тестов размещает петлю обратной связи в коде теста – учет покрытия во время генерации тестов позволяет быстрее достигать требуемого покрытия путем автоматической генерации более направленных тестов. Здесь описывается метод реализации этого принципа, используемый при изолированной верификации модулей микропроцессоров серии «Эльбрус».

Подробнее... Загрузить файл ![]()

Содержание:

Введение

1. Генератор тестов, управляемый покрытием

2. Генерация RTL-модели

3. Измерение покрытия

4. Экспериментальные результаты

Заключение

Литература

Опыт реализации системы верификации, управляемой тестовым покрытием

Опыт реализации системы верификации, управляемой тестовым покрытиемПредложен метод генерации тестов изолированных устройств, использующий измеряемую во время генерации величину покрытия для увеличения эффективности тестирования. Для обеспечения высокой скорости измерения во время генерации и работы с состоянием модели в качестве средства генерации RTL-модели использован транслятор Verilog-кода в C++.