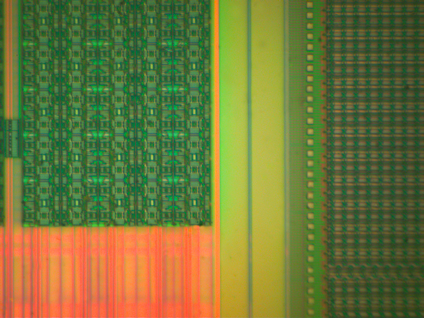

Особенности физического проектирования микропроцессоров на базе 90-нм технологий

За последние годы плотность интеграции и быстродействие интегральных микросхем, особенно микропроцессоров, выросли многократно. С увеличением этих параметров существенно возрастает и трудоемкость проектирования СБИС. Из-за увеличения числа транзисторов критически важным в достижении коммерческого успеха становится время проектирования изделия, что вызвало появление иерархического подхода к его разработке. Переход на нанотехнологии (менее 100 нм) и повышение быстродействия требуют учета металлических межсоединений и более тонких эффектов в полупроводниках, что возможно только в современных САПР. Из-за высокой стоимости изготовления СБИС на фабрике необходимо придерживаться жестких методологий проектирования и стратегий, которые более податливы автоматизации процесса проектирования, чтобы избежать возможных ошибок и повысить коэффициент выхода годных. В статье рассмотрены особенности физического проектирования микропроцессоров с технологическими нормами 90 нм в ЗАО «МЦСТ»

Подробнее... Загрузить файл ![]()

Содержание:

Введение

1. Планирование топологии кристалла на этапе физического проектирования

2. Особенности проектирования верхнего уровня иерархии системы для кристалла с архитектурой «ЭЛЬБРУС»

3. Снижение потребляемой мощности

4. Проблемы повышения выхода годных микросхем

Литература

Особенности физического проектирования микропроцессоров на базе 90-нм технологий

Особенности физического проектирования микропроцессоров на базе 90-нм технологийСопоставляются плоский и иерархический методы проектирования СБИС, их преимущества и недостатки. Особое внимание уделено иерархическому методу, позволяющему добиться более качественного планирования кристалла, улучшения временных характеристик и сокращения времени проектирования.